- 您现在的位置:买卖IC网 > Sheet目录1223 > KIT10XS3535EVBE (Freescale Semiconductor)KIT EVAL BOARD FOR 10XS3535

�� �

�

FUNCTIONAL� DEVICE� OPERATION�

�LOGIC� COMMANDS� AND� REGISTERS�

�ADDRESS� 00011� —� CONFIGURATION� CSNS�

�The� Configuration� Current� Sense� register� is� used� to�

�disable� the� high� over-current� shutdown� phase� (OCHI1� and�

�OCHI2� dynamic� levels)� in� order� to� activate� immediately� the�

�current� sense� analog� feedback.�

�When� bit� D9� is� set� to� logic� [1],� the� current� sense�

�synchronization� signal� is� reported� on� FETOUT� output� pin.�

�When� the� corresponding� NO_OCHI� bit� is� set� to� logic� [1],�

�the� output� is� only� protected� with� OCLO� level.� And� the� current�

�sense� is� immediately� available� if� it� is� selected� through� SPI,� as�

�described� in� Figures 13� .� The� NO_OCHI� bit� per� output� is�

�automatically� reset� at� each� corresponding� ONoff� bit� transition�

�from� logic� [1]� to� [0]� and� in� case� of� over-temperature� or� over-�

�current� fault.� All� NO_OCHI� bits� are� also� reset� in� case� of�

�under-voltage� fault� detection.�

�ADDRESS� 01001� —� CONTROL� OUT1�

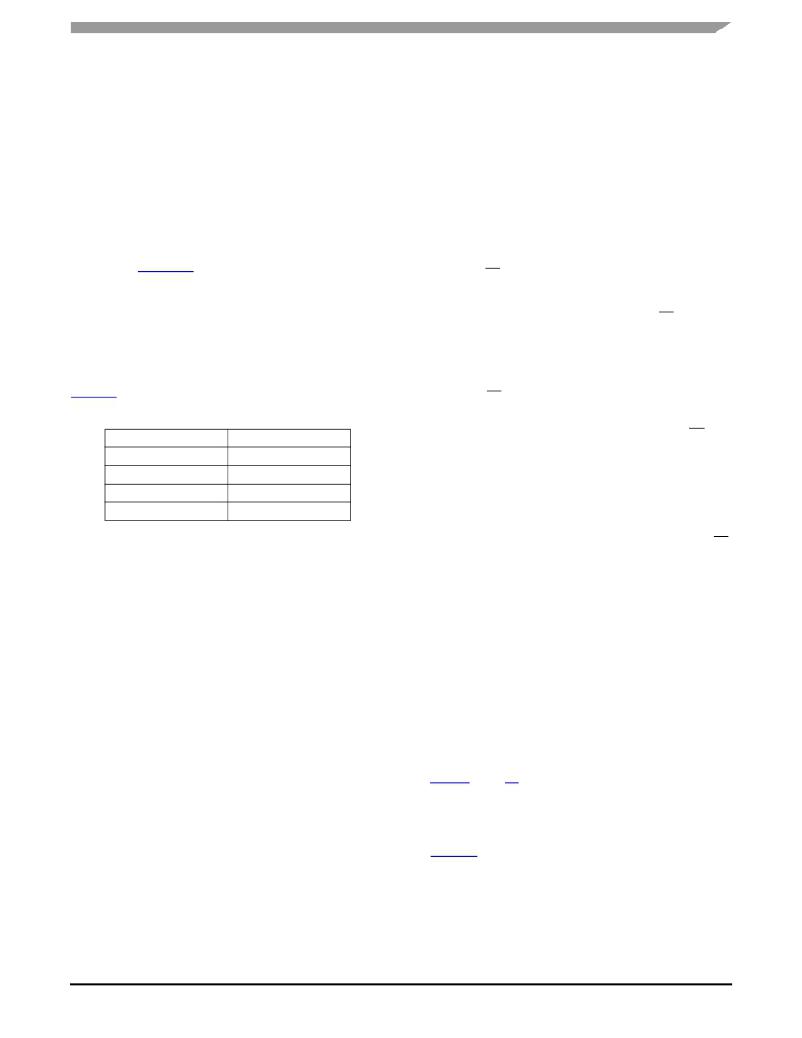

�Bits� D9� and� D8� control� the� switching� phases� as� shown� in�

��Table� 10.� Switching� Phases�

�ADDRESS� 01110� —� CONTROL� EXTERNAL� SWITCH�

�Same� description� as� OUT1.�

�ADDRESS� 01111� —� TEST� MODE�

�This� register� is� reserved� for� test� and� is� not� available� with�

�SPI� during� normal� operation.�

�SERIAL� OUTPUT� COMMUNICATION� (DEVICE�

�STATUS� RETURN� ?�

�DATA)�

�When� the� CS� pin� is� pulled� low,� the� output� register� is�

�loaded.� Meanwhile,� the� data� is� clocked� out� MSB� first� as� the�

�new� message� data� is� clocked� into� the� SI� pin.� The� first� 16� bits�

�of� data� clocking� out� of� the� SO,� and� following� a� CS� transition,�

�is� dependant� upon� the� previously� written� SPI� word� (SOA1�

�and� SOA0� defined� in� the� last� SPI� initialization� word).�

�Any� bits� clocked� out� of� the� SO� pin� after� the� first� 16� will� be�

�representative� of� the� initial� message� bits� clocked� into� the� SI�

�pin� since� the� CS� pin� first� transitioned� to� a� logic� [0].� This�

�feature� is� useful� for� daisy� chaining� devices.�

�D9� :� D8�

�00�

�01�

�10�

�11�

�PWM� Phase�

�0°�

�90°�

�180°�

�270°�

�A� valid� message� length� is� determined� following� a� CS�

�transition� of� logic� [0]� to� logic� [1].� If� the� message� length� is�

�valid,� the� data� is� latched� into� the� appropriate� registers.� A� valid�

�message� length� is� a� multiple� of� 16� bits.� At� this� time,� the� SO�

�pin� is� tri-stated� and� the� fault� status� register� is� now� able� to�

�accept� new� fault� status� information.�

�Bit� D7� at� logic� [1]� turns� ON� OUT1.� OUT1� is� turned� OFF�

�with� bit� D7� at� logic� [0].� This� register� allows� the� master� to�

�control� the� duty� cycle� and� the� switching� phases� of� OUT1.� The�

�duty� cycle� resolution� is� given� by� bits� D6� :� D0.�

�D7� =� 0,� D6� :� D0� =� XX� output� OFF.�

�D7� =� 1,� D6� :� D0� =� 00� output� ON� during� 1/128.�

�D7� =� 1,� D6� :� D0� =� 1A� output� ON� during� 27/128� on� PWM�

�period.�

�D7� =� 1,� D6� :� D0� =� 7F� output� continuous� ON� (no� PWM).�

�ADDRESS� 01010� —� CONTROL� OUT2�

�Same� description� as� OUT1.�

�ADDRESS� 01011� —� CONTROL� OUT3�

�Same� description� as� OUT1.�

�ADDRESS� 01100� —� CONTROL� OUT4�

�Same� description� as� OUT1.�

�ADDRESS� 01101� —� CONTROL� OUT5�

�The� output� status� register� correctly� reflects� the� status� of�

�the� Initialization-selected� register� data� at� the� time� that� the� CS�

�is� pulled� to� a� logic� [0]� during� SPI� communication� and� /� or� for�

�the� period� of� time� since� the� last� valid� SPI� communication,�

�with� the� following� exceptions:�

�?The� previous� SPI� communication� was� determined� to� be�

�invalid.� In� this� case,� the� status� will� be� reported� as�

�though� the� invalid� SPI� communication� never� occurred.�

�?Battery� transients� below� 6.0� V,� resulting� in� an� under-�

�voltage� shutdown� of� the� outputs,� may� result� in� incorrect�

�data� loaded� into� the� SPI� register,� except� the� UVF� fault�

�reporting� (OD13).�

�SERIAL� OUTPUT� BIT� ASSIGNMENT�

�The� contents� of� bits� OD15� :� OD0� depend� on� bits� D1:� D0�

�from� the� most� recent� initialization� command� SOA[1:0]� (refer�

�to� Table 8� ,� page� 29� ),� as� explained� in� the� paragraphs� that�

�follow.�

�The� register� bits� are� reset� by� a� read� operation� and� also� if�

�the� fault� is� removed.�

�Table 11� summarizes� the� SO� register� content.� Bit� OD10�

�reflects� Normal� mode� (NM).�

�Same� description� as� OUT1.�

�MC10XS3535�

�Analog� Integrated� Circuit� Device� Data� ?�

�Freescale� Semiconductor�

�31�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

KIT13892VLEVBEJ

KIT EVAL FOR MC13892

KIT17C724EPEVBE

KIT FOR 17C7242CH HBRIDGE PWR IC

KIT33810EKEVME

BOARD EVAL FOR MC33810

KIT33811EGEVBE

KIT EVAL 33811 SOLENOID MON IC

KIT33812ECUEVME

KIT DESIGN FOR 33812/S12P

KIT33812EKEVBE

BOARD EVALUATION FOR MC33812

KIT33879AEKEVBE

BOARD EVALUATION FOR MC33879

KIT33880DWBEVB

KIT EVAL FOR MC33880 8X SW W/SPI

相关代理商/技术参数

KIT10XS4200EVBE

制造商:Freescale Semiconductor 功能描述:EVAL BOARD, MC10XS4200 HIGH SIDE SWITCH; Silicon Manufacturer:Freescale; Silicon Core Number:MC10XS4200; Kit Application Type:High Side Switch; Application Sub Type:-; Kit Contents:Eval Board MC10XS4200, CD ROM

KIT-1113C

制造商:ABIKO 功能描述:Bulk

KIT1116-400

制造商:Laird Technologies Inc 功能描述:ANTKIT,FG 128-137MHZ/ODB + FM2

KIT-113-175C

制造商:LG Corporation 功能描述:KIT TUNER 113-175C (113-175E +

KIT1133-P250

功能描述:ANTKIT GB8W15FT CABLE 制造商:laird technologies ias 系列:* 零件状态:在售 标准包装:1

KIT-11591

功能描述:ISP POGO ADAPTER KIT 制造商:sparkfun electronics 系列:- 零件状态:在售 套件类型:初级入门套件 主要用途:ISP Pogo 适配器 标准包装:1

KIT1167-120

制造商:Laird Technologies Inc 功能描述:ANT KIT GPS1575PW 20FT 制造商:Laird Technologies Inc 功能描述:ANTKIT,GPS1575PW/20FT

KIT1185-120

制造商:Laird Technologies Inc 功能描述:KIT ANT GPS 20FT 制造商:Laird Technologies Inc 功能描述:KIT1185-120